# Signal Processing MAGAZINE

VOLUME 27 NUMBER 2 MARCH 2010

# MULTICORE PLATFORMS RIDING THE WAVE OF TOMORROW, PART 2

THE CURVELET TRANSFORM

SETI-**ARE WE ALONE?**

A FLEXIBLE WINDOW FUNCTION

**Click here** to access

# ontent Gazette

Supplement

# +20 dBm Power Amplifiers with a choice of gain!

Mini-Circuits' monolithic, surface-mount GVA amplifiers are extremely broadband, with wide dynamic range and the right gain to fit your application. Based on high-performance InGaP HBT technology, patented GVA amplifiers cover DC\* to 7 GHz, with a selection of gain choices 10, 15, 20 or 24dB, (measured at 1 GHz). They provide better than +20 dBm typical output power, with typical IP3 performance as high

US patent 6,943,629 \*Low frequency determined by coupling cap.

as +41 dBm at 1 GHz. Supplied in RoHS-compliant, SOT-89 housings, low-cost GVA amplifiers feature excellent input/output return loss and high reverse isolation. With built-in ESD protection, GVA amplifiers are unconditionally stable and designed for a single 5-V supply. For more on broadband GVA amplifiers, visit the Mini-Circuits' web site at <u>www.minicircuits.com</u>.

Mini-Circuits...Your partners for success since 1969

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661

The Design Engineers Search Engine finds the model you need, Instantly • For detailed performance specs & shopping online see

IF/RF MICROWAVE COMPONENTS

458 rev C

Mass

VOLUME 27 NUMBER 2

# CONTENTS

### SPECIAL SECTION—SIGNAL PROCESSING ON PLATFORMS WITH MULTIPLE CORES, PART 2

- **20 FROM THE GUEST EDITORS** Yen-Kuang Chen, Chaitali Chakrabarti, Shuvra Bhattacharyya, and Bruno Bougard

- 22 FUTURE SOFTWARE-DEFINED **RADIO PLATFORMS** AND MAPPING FLOWS

Martin Palkovic, Praveen Raghavan, Min Li, Antoine Dejonghe, Liesbet Van der Perre, and Francky Catthoor

- **34 AN ADVANTAGEOUS ROTOSCOPING METHOD** Richard Rzeszutek, Thomas F. El-Maraghi, Dimitrios Androutsos, and Samuel Zhou

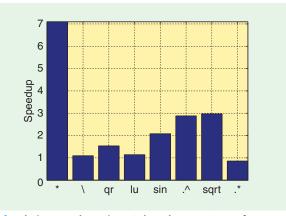

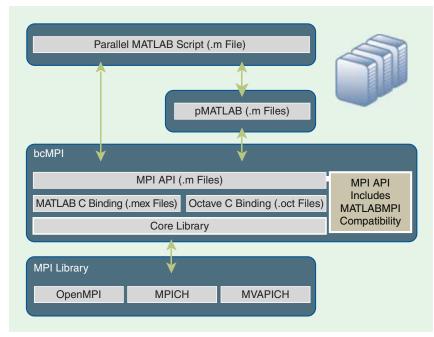

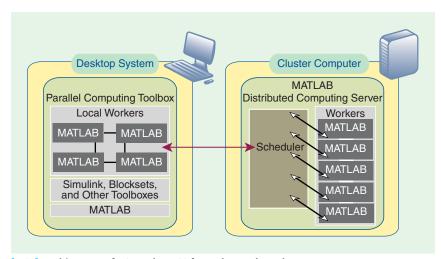

- 40 MATLAB FOR SIGNAL **PROCESSING ON** MULTIPROCESSORS AND **MULTICORES**

Siddharth Samsi, Vijay Gadepally, and Ashok Krishnamurthy

COVER CHAD BAKER/DIGITAL VISION/

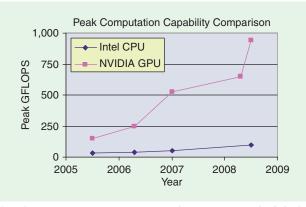

50 A SURVEY OF MEDICAL IMAGE **REGISTRATION ON MULTICORE** AND THE GPU

Ramtin Shams, Parastoo Sadeghi, Rodney A. Kennedy, and Richard I. Hartley

- 61 UTILIZING HIERARCHICAL MULTIPROCESSING FOR MEDICAL IMAGE REGISTRATION William Plishker, Omkar Dandekar, Shuvra S. Bhattacharyya, and Raj Shekhar

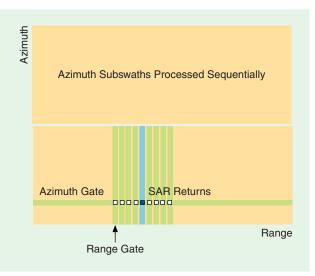

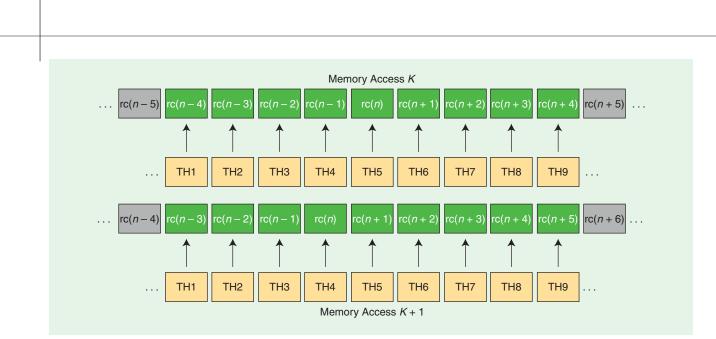

- **69 SYNTHETIC APERTURE RADAR** PROCESSING WITH GPGPU Maurizio di Bisceglie, Michele Di Santo, Carmela Galdi, Riccardo Lanari, and Nadia Ranaldo

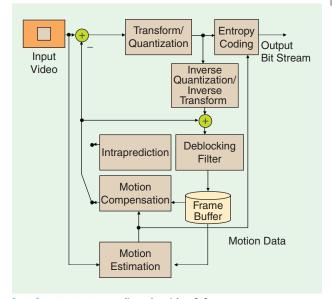

- 79 VIDEO CODING ON MULTICORE **GRAPHICS PROCESSORS** Ngai-Man Cheung, Xiaopeng Fan, Oscar C. Au, and Man-Cheung Kung

- 90 AUDIO SPARSE **DECOMPOSITIONS IN PARALLEL** Laurent Daudet

- 97 IMAGE PROCESSING ON **MULTICORE x86 ARCHITECTURES** Daehyun Kim, Victor W. Lee, and Yen-Kuang Chen

- 108 BUILDING CORRELATORS WITH MANY-CORE HARDWARE Rob V. van Nieuwpoort

and John W. Romein

SCOPE: IEEE Signal Processing Magazine publishes tutorial-style articles on signal processing research and applications, as well as columns and forums on issues of interest. Its coverage ranges from fundamental principles to practical implementation, reflecting the multidimensional facets of interests and concerns of the community. Its mission is to bring up-to-date, emerging and active technical developments, issues, and events to the research, educational, and professional communities. It is also the main Society communication platform addressing important issues concerning all members.

IEEE SIGNAL PROCESSING MAGAZINE (ISSN 1053-5888) (ISPREG) is published bimonthly by the Institute of Electrical and Electronics Engineers, Inc., 3 Park Avenue, 17th Floor, New York, NY 10016-5997 USA (+1 212 419 7900). Responsibility for the contents rests upon the authors and not the IEEE, the Society, or its members. Annual member subscriptions included in Society fee. Nonmember subscriptions available upon request. Individual copies: IEEE Members \$20.00 (first copy only), non-members \$175.00 per copy. Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limits of U.S. Copyright Law for private use of patrons: 1) those post-1977 articles that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923 USA; 2) pre-1978 articles without fee. Instructors are permitted to photocopy isolated articles for noncommercial classroom use without fee. For all other copying, reprint, or republication permission, write to IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08854 USA. Copyright©2010 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Periodicals postage paid at New York, NY, and at additional mailing offices. Postmaster: Send address changes to IEEE Signal Processing Magazine, IEEE, 445 Hoes Lane, Piscataway, NJ 08854 USA Canadian GST #125634188 Printed in the U.S.A.

Digital Object Identifier 10.1109/MSP.2009.935379

# **FEATURE**

**118 THE CURVELET TRANSFORM** Jianwei Ma and Gerlind Plonka

# **COLUMNS**

- **2** FROM THE EDITOR New Focus, New Challenge Li Deng

- 4 PRESIDENT'S MESSAGE SPS: Forging Ahead with New Innovations for Its Members Mostafa (Mos) Kaveh

- **12 SPOTLIGHT REPORT** SETI-Are We (Still) Alone? Ron Schneiderman

- **16 READER'S CHOICE** Top Downloads in IEEE Xplore

- **134 APPLICATIONS CORNER** Multicore Image Processing with OpenMP Greg Slabaugh, Richard Boyes, and Xiaoyun Yang

- 139 DSP TIPS&TRICKS A Flexible Window Function for Spectral Analysis Tae Hyun Yoon and Eon Kyeong Joo

- **143 LECTURE NOTES**

The Phased Array Is the Maximum SNR Active Array Jian Li and Petre Stoica

#### 145 BEST OF THE WEB

DataWare: Sea Clutter and Small Boat Radar Reflectivity Databases H.J. de Wind, J.C. Cilliers, and P.L. Herselman

#### 149 DSP FORUM

Ultra-Low Power Signal Processing Gene Frantz, Jörg Henkel, Jan Rabaey, Todd Schneider, Marilyn Wolf, and Umit Batur

**160 IN THE SPOTLIGHT** Paths Ahead in the Science of Information and Decision Systems Alan S. Willsky

### DEPARTMENTS

- 6 SOCIETY NEWS

- **155 DATES AHEAD**

IEEE SIGNAL PROCESSING MAGAZINE [1] MARCH 2010

### from the **EDITOR**

CMags

### New Focus, New Challenge

apid advancement of our information society necessitates prompt update and expansion of the technical scope and focus of interest of our IEEE Signal Processing Society (SPS). Compared with just some years ago, the current focus of signal processing as an enabling technology has been significantly broadened. Now it encompasses theories, architectures, algorithms, implementations, and applications for the transformation of information contained in many different physical, symbolic, or abstract formats that we broadly designate as "signals." Methodology wise, signal processing uses mathematical,

Digital Object Identifier 10.1109/MSP.2009.935593

statistical, computational, heuristic, and/ or linguistic representations, formalisms, and techniques for sensing, acquisition, extraction, representation, modeling, analysis, synthesis, compression, detection, recovery, decomposition, enhancement, rendering, display, learning, recognition, understanding, securing, authenticating, and communicating of information and signals. Such diverse "processing" tasks are accomplished by either digital or analog devices or algorithms, and in the form of either software, hardware, or firmware.

New elements in the updated focus of interest above are reflected particularly by the expanded members of the "signal," as pursued currently by a wide range of work of the SPS's 11 technical areas. The updated "signal" members cover any abstract, symbolic, or physical manifestation of information with examples that include: audio, music, speech, text, image, graphics, video, multimedia, sensor, communication, geophysical, sonar, radar, biological, chemical, molecular, genomic, medical, data, or sequences of symbols, attributes, or numerical quantities.

The expanded technical scope of our Society presents new challenges for *IEEE Signal Processing Magazine*, especially with respect to its role of educating our readers in new trends and in cross-pollinating technical areas. Signal processing is a vibrant and inherently

(continued on page 148)

#### IEEE SIGNAL PROCESSING MAGAZINE Li Deng, Editor-in-Chief — Microsoft Research

#### AREA EDITORS

Feature Articles -- Antonio Ortega, University of Southern California humps and Forums — Ghassan AlRegib, Columns and Forums -Georgia Institute of Technology Special Issues — Dan Schonfeld, University of Illinois at Chicago e-Newsletter -– Min Wu, University of Maryland EDITORIAL BOARD Alex Acero — Microsoft Research John G. Apostolopoulos - Hewlett-Packard Laboratories Les Atlas - University of Washington Jeff Bilmes - University of Washington Holger Boche — Fraunhofer HHL Germany Liang-Gee Chen — National Taiwan University Ed Delp - Purdue University Adriana Dumitras — Apple Inc. Brendan Frey - University of Toronto Sadaoki Furui — Tokyo Institute of Technology,

Japan Alex Gershman — Darmstadt University of Technology, Germany Mazin Gilbert — AT&T Research

Jenq-Neng Hwang — University of Washington Alex Kot — Nanyang Technological University, Singapore

Vikram Krishnamurthy — University of British Columbia, Canada Chin-Hui Lee — Georgia Institute of Technology

Chini-Hui Lee — Georgia Institute of Technology

Digital Object Identifier 10.1109/MSP.2010.936095

Jian Li — University of Florida-Gainesville Tom Luo — University of Minnesota Soo-Chang Pei — National Taiwan University Fernando Pereira — ISTIT, Portugal Roberto Pieraccini — Speech Cycle Inc. Majid Rabbani — Eastman Kodak Company Phillip A. Regalia — Catholic University of America Nicholas Sidiropoulos — Tech University of Crete, Greece Yoram Singer — Google Research Henry Tirri — Nokia Research Center Anthony Vetro — MERL Xiaodong Wang — Columbia University Patrick J. Wolfe — Harvard University

#### ASSOCIATE EDITORS

COLUMNS AND FORUM Umit Batur — Texas Instruments Andrea Cavallaro — Queen Mary, University of London Berna Erol — Ricoh California Research Center

- Rodrigo Capobianco Guido University of Sao Paulo, Brazil Konstantinos Konstantinides — Hewlett-Packard

- Andres Kwasinski Rochester Institute of Technology

- Rick Lyons Besser Associates Aleksandra Mojsilovic — IBM T.J. Watson Research Center George Moschytz — Bar-Ilan University, Israel Douglas O'Shaughnessy — INRS, Canada C. Britton Rorabaugh — DRS C3 Systems Co.

C. Britton Rorabaugh — DRS C3 Systems Co. Greg Slabaugh — Medicsight PLC, U.K.

Wade Trape — Rutgers University Stephen T.C. Wong — Methodist Hospital-Cornell Dong Yu — Microsoft Research Pascal Frossard — EPFL, Switzerland Yan Lindsay Sun — University of Rhode Island Z. Jane Wang — University of British Columbia, Canada IEEE PERIODICALS MAGAZINES DEPARTMENT Geraldine Krolin-Taylor -- Senior Managing Editor Jessica Barragué--Associate Editor Susan Schneiderman - Business Development Manager +1 732 562 3946 Fax: +1 732 981 1855 Felicia Spagnoli – Advertising Production Mgr. Feitca Spagnon — Autor Long Janet Dudar — Senior Art Director Gail A. Schnitzer — Assistant Art Director Theresa L. Smith — Production Coordinator Dawn M. Melley -Peter M. Tuohy -Editorial Director - Production Director Fran Zappulla Staff Director, Publishing

ASSOCIATE EDITORS—E-NEWSLETTER Nitin Chandrachoodan — India Institute

of Technologies

#### IEEE prohibits discrimination, harassment, and bullying. For more information, visit <u>http://www.ieee.org/web/</u>

Operations

aboutus/whatis/policies/p9-26.html. IEEE SIGNAL PROCESSING SOCIETY Mos Kaveh — President K.J. Ray Liu — President-Elect Michael D. Zoltowski — Vice President, Awards and Membership V. John Mathews — Vice President, Conferences Min Wu — Vice President, Finance Ali H. Sayed — Vice President, Fublications Ahmed Tewfik — Vice President, Technical Directions Mercy Kowalczyk — Executive Director and Associate Editor

IEEE SIGNAL PROCESSING MAGAZINE [2] MARCH 2010

For Commercial, Military, and Industrial Use, Mini-Circuits proudly presents the MCA1 series of Low Temperature Co-fired Ceramic (LTCC) frequency mixers. Highly reliable, only 0.080" in height, and "tough as nails", these patented mixers have all circuitry hermetically imbedded inside the ceramic making them temperature stable and impervious to most environmental conditions. The process also gives you high performance repeatability and very low cost. There's a variety of broadband models and LO power levels to choose from, so you can use these mixers in a multitude of designs and applications. And MCA1 mixers are ideal for the COTS program! Just check all the specs on our web site. Then, choose the model that best fits your needs. Our team is ready to handle your requirements with quick off-the-shelf shipments, custom designs, and fast turn-around/high volume production.

Mini-Circuits...Your partners for success since 1969

For RoHS compliant requirements, ADD + SUFFIX TO BASE MODEL No. Example: MCA1-85L+

|                                                 | IVIOUEI     | LO      | Fieq.      | COIN. | LO-NF | FIICE     |  |  |  |  |

|-------------------------------------------------|-------------|---------|------------|-------|-------|-----------|--|--|--|--|

|                                                 |             | Level   | Range      | Loss  | Isol. | \$ ea.    |  |  |  |  |

|                                                 |             | (dBm)   | (MHž)      | (dB)  | (dB)  | (Qty. 10) |  |  |  |  |

|                                                 | MCA1-85L    | 4       | 2800-8500  | 6.0   | 35    | 9.45      |  |  |  |  |

|                                                 | MCA1-12GL   | 4       | 3800-12000 | 6.5   | 38    | 11.95     |  |  |  |  |

|                                                 | MCA1-24     | 7       | 300-2400   | 6.1   | 40    | 5.95      |  |  |  |  |

|                                                 | MCA1-42     | 7       | 1000-4200  | 6.1   | 35    | 6.95      |  |  |  |  |

|                                                 | MCA1-60     | 7       | 1600-6000  | 6.2   | 30    | 7.95      |  |  |  |  |

|                                                 | MCA1-85     | 7       | 2800-8500  | 5.6   | 38    | 8.95      |  |  |  |  |

|                                                 | MCA1-12G    | 7       | 3800-12000 | 6.2   | 38    | 10.95     |  |  |  |  |

|                                                 | MCA1-24LH   | 10      | 300-2400   | 6.5   | 40    | 6.45      |  |  |  |  |

|                                                 | MCA1-42LH   | 10      | 1000-4200  | 6.0   | 38    | 7.45      |  |  |  |  |

|                                                 | MCA1-60LH   | 10      | 1700-6000  | 6.3   | 30    | 8.45      |  |  |  |  |

|                                                 | MCA1-80LH   | 10      | 2800-8000  | 5.9   | 35    | 9.95      |  |  |  |  |

|                                                 | MCA1-24MH   | 13      | 300-2400   | 6.1   | 40    | 6.95      |  |  |  |  |

|                                                 | MCA1-42MH   | 13      | 1000-4200  | 6.2   | 35    | 7.95      |  |  |  |  |

|                                                 | MCA1-60MH   | 13      | 1600-6000  | 6.4   | 27    | 8.95      |  |  |  |  |

|                                                 | MCA1-80MH   | 13      | 2800-8000  | 5.7   | 27    | 10.95     |  |  |  |  |

|                                                 | MCA1-80H    | 17      | 2800-8000  | 6.3   | 34    | 11.95     |  |  |  |  |

| Dimensions: (L) 0.30" x (W) 0.250" x (H) 0.080" |             |         |            |       |       |           |  |  |  |  |

|                                                 | U.S. Patent | #7,027, | 795        |       |       |           |  |  |  |  |

|                                                 |             |         |            |       |       |           |  |  |  |  |

1000)

Conv. LO DE Drior

tr∩n

**Nini-Circuits** ISO 9001 ISO 14001 AS 9100 CERTIFIED

P.O. Box 350166, Brooklyn, New York 11235-0003 (718) 934-4500 Fax (718) 332-4661

The Design Engineers Search Engine finds the model you need, Instantly • For detailed performance specs & shopping online see

**IF/RF MICROWAVE COMPONENTS**

385 rev M

CMass

president's **MESSAGE**

CMags

# SPS: Forging Ahead with New Innovations for Its Members

had the good fortune to join some 1,200 attendees from around the world by participating in the recordsetting 2009 IEEE International Conference on Image Processing in Cairo, Egypt. I congratulate General Chair Prof. Magdy Bayoumi and his conference organizing committee for a terrific program and a superb venue. The outstanding technical program was complemented by Egyptian hospitality fit for the pharaohs and the opportunity for attendees to experience transcendent historical and cultural treasures. As the first major event for the Society on the African continent, the conference underscored the IEEE Signal Processing Society's (SPS's) renewed emphasis on regional member development and engagement, reflected most visibly by the planned addition of four elected regional directors to its Board of Governors (BoG).

The Cairo meeting also provided the opportunity for the BoG to review and approve a number of recommendations by the Society's boards and ad hoc volunteer and staff committees. The Society's governance is codified in its Constitution, and the organization operates under its Bylaws, which are aided by a set of policies and procedures. In the January 2010 issue of IEEE Signal Processing Magazine, Past President José Moura reported on the work of an ad hoc committee of volunteers and staff chaired by President-Elect Ray Liu that had carried out a significant update of the bylaws and policies and procedures. As José had anticipated, the BoG approved these recommendations, which establish clear collaboration and report-

Digital Object Identifier 10.1109/MSP.2009.935594

ing structures for volunteer leaders and staff. The approved documents expand and make more open and transparent the nominations for Society elections. They also increase the portfolio of the vice president of awards and membership to include the awards board with its Fellow Reference Committee, and the membership board, which now includes the Industrial Relations Committee, the new Membership Services Committee, and the Chapters Standing Committee.

#### THE WORK OF THE SOCIETY'S VOLUNTEERS, **STAFF, AND ITS OPERATIONS, PROGRAMS, PRODUCTS,** AND SERVICES RECEIVED **OUTSTANDING MARKS BY** THE REVIEW COMMITTEE AT TAB'S NOVEMBER 2009 MEETING.

The governance of the membership services committee, in turn, includes the aforementioned four regionally elected directors. The updated Bylaws are more concise, clear, and consistent, and the new policies and procedures provide the detail necessary to manage the enterprise, and at the same time, are amenable to updating as necessary for a dynamic field such as signal processing.

The BoG also had the opportunity to honor the Society's 1994-1995 president, Prof. Tariq Durrani, OBE, on the occasion of his retirement from the faculty and long-time academic leadership at Strathclyde University in Glasgow, Scotland. The BoG adopted a resolution recognizing Prof. Durrani's significant contributions to the field and the Society (and, indeed, the IEEE).

Another endorsement of honors by the BoG was the election of the Distinguished Lecturers for 2010-2011 (see the "Society News" column on page 6). Congratulations to our colleagues Sheila Hemami, Shrikanth Narayanan, Antonio Ortega, Venu Veeravalli, and Abdelhak Zoubir.

Last summer, the SPS underwent its mandated five-year review by the IEEE Technical Activities Board (TAB). The work of the Society's volunteers, staff, and its operations, programs, products, and services received outstanding marks by the review committee at TAB's November 2009 meeting. It is easy to be complacent in the face of such accomplishments and accolades. But the SPS continues to forge ahead with new innovations and services for its members and the broader community. As Society members, you are now receiving electronic access to SPS publications as part of your membership dues, and digital delivery of SPS publications has been approved for 2010. The inaugural IEEE Thematic Meetings on Signal Processing (THEMES) will take place the week of 15 March 2010 in conjunction with the IEEE International Conference on Acoustics, Speech, and Signal Processing in Dallas, Texas. The Society is also pursuing active involvement in IEEE's Smart Grid Initiative. We are interested in learning of activities in our field that have been applied to this energy-related topic. I look forward to seeing many of you in Dallas and/or hearing your suggestions by e-mail.

SP

# A new era, a new New tracks. New courses. New focus.

ESC Silicon Valley brings together systems architects, design engineers, suppliers, analysts, and media from across the globe. With cutting edge product demonstrations, visionary keynotes, and hundreds of essential training classes, ESC is the ideal conference for the embedded design community to learn, collaborate, and recognize excellence.

ESC Silicon Valley 2010 features:

- Two "Build Your Own Embedded System" programs featuring the new Intel Multicore Atom and the Freescale Tower development system

- Multicore Expo and Conference co-located with ESC Silicon Valley

- ARM Partner Pavilion

- Display and Connected Devices Emerging Technology Zones

- Keynotes from Dr. Michio Kaku, theoretical physicist and bestselling author and Richard Templeton, CEO & President, Texas Instruments

Start your own personal development at ESC 2010. You can't afford to miss it.

Silicon Valley McEnery Convention Center, San Jose, April 26 - 29, 2010 Conference: April 26 - 29, 2010 Expo: April 27 – 29, 2010

Register Today. www. embedded.com/sv

CMass

### society NEWS

# Distinguished Lecturers, Fellows, Awards, and Calls for Nominations

n this column, profiles are given for the IEEE Signal Processing Society's (SPS's) 2010 class of Distinguished Lecturers, the 2010 SPS Fellows are introduced, award recipients are announced, and nominations are sought for directors-at-large and Board of Governors members-at-large.

#### 2010 CLASS OF DISTINGUISHED LECTURERS

The SPS's Distinguished Lecturer Program provides the means for Chapters to have access to well-known educators and authors in the fields of signal processing to lecture at Chapter meetings. Chapters interested in arranging lectures by the Distinguished Lecturers can obtain information from the Society's Web page (http:// www.signalprocessingsociety.org/lecturers/ distinguished-lecturers/) or by sending an e-mail to sp.info@ieee.org.

Candidates for the Distinguished Lecturer Program are solicited from the Society Technical Committees, Editorial Boards, and Chapters by the Awards Board. The Awards Board vets the nominations, and the Board of Governors approves the final selection. Distinguished Lecturers are appointed for a term of two calendar years.

#### 2010 DISTINGUISHED LECTURERS

#### SHEILA S. HEMAMI

Sheila S. Hemami received the B.S.E.E. degree from the University of Michigan in 1990 and the M.S.E.E. and Ph.D. degrees from Stanford University in 1992 and 1994, respectively. Her Ph.D. thesis was "Reconstruction of Compressed Images and Video for Lossy Packet Networks," and she was one of the first researchers to work on what we now call error concealment. In

Digital Object Identifier 10.1109/MSP.2009.935586

1994, she was with Hewlett-Packard Laboratories, Palo Alto, California. She joined the School of Electrical Engineering at Cornell University in 1995, where she is a professor and directs the Visual Communications Laboratory.

Dr. Hemami's research interests broadly concern communication of visual information, both from a signal processing perspective (signal representation, source coding, and related issues) and from a psychophysical perspective.

Dr. Hemami is an IEEE Fellow and has held various visiting positions, most recently at the University of Nantes, France, and Ecole Polytechnique Federale de Lausanne, Switzerland. She has received numerous college and national teaching awards, including Eta Kappa Nu's C. Holmes MacDonald Award. She is editorin-chief of IEEE Transactions on Multimedia (2008-2010); member-at-large of the SPS Board of Governors (2009-2011), and an SPS Distinguished Lecturer (2010-2011). She chaired the IEEE Image and Multidimensional Signal Processing Technical Committee (2006-2007) and was associate editor for IEEE Transactions on Signal Processing (2000-2006).

Dr. Hemami's lecture topics include the following:

- "From Single Media to Multimedia— Perception, Coding, and Quality"

- "A Signal-Processing Approach to Modeling Vision and Applications"

- "Task-Based Imaging—Image Usefulness and Its Relationship to Image Quality."

#### SHRIKANTH NARAYANAN

Shrikanth Narayanan received his M.S., Engineer, and Ph.D. degrees in electrical engineering, from the University of California, Los Angeles, in 1990, 1992, and 1995, respectively. He is the Andrew J. Viterbi Professor of Engineering at the University of Southern California (USC), where he has been since 2000, and professor in the Signal and Image Processing Institute of USC's Electrical Engineering Department. He also holds joint appointments as professor in computer science, linguistics and psychology. From 1995 to 2000, he was with AT&T, first as a senior member and later as a principal member of its technical staff.

CMags

Dr. Narayanan is editor, Computer, Speech and Language Journal, and associate editor, IEEE Transactions on Multimedia (2009) and the Journal of Acoustical Society of America. He was also associate editor. IEEE Transactions of Speech and Audio Processing (2000–2004) and IEEE Signal Processing Magazine (2005-2008). He is on the Speech Communication and Acoustic Standards Committees of the Acoustical Society of America and the Advisory Council of the International Speech Communication Association. He served on the SPS Speech Processing Technical Committee (2003-2007) and the SPS Multimedia Signal Processing Technical Committee (2005–2008).

He is an IEEE Fellow: fellow. Acoustical Society of America; and member, Tau Beta Pi, Phi Kappa Phi, and Eta Kappa Nu. He is the recipient of an NSF CAREER Award, USC Engineering Junior Research Award, USC Electrical Engineering Northrop-Grumman Research Award, Mellon Award for Mentoring Excellence, Okawa Research Award, IBM Faculty Award, and a faculty fellowship from the USC Center for interdisciplinary research. He received the 2005 SPS Best Paper Award. Papers coauthored with his students have won awards at InterSpeech 2009 Emotion Challenge, IEEE DCOSS 2009, IEEE MMSP 2007, IEEE MMSP 2006, ICASSP 2005, and ICSLP 2002.

His research interests are in signals and systems modeling with an interdisciplinary emphasis on speech, audio, language;

IEEE SIGNAL PROCESSING MAGAZINE [6] MARCH 2010

# **Discover These New Titles from Wiley and Wiley-IEEE Press**

#### Advanced Signal Integrity for High-Speed Digital Designs Stephen H. Hall, Howard L. Heck

9780470192351 • Cloth • 680pp • \$120.00 • March 2009 Wiley-IEEE Press

This book is designed to provide contemporary readers with an understanding of the emerging high-speed signal integrity issues that are creating roadblocks in digital design. Written by the foremost experts on the subject, it leverages

concepts and techniques from non-related fields such as applied physics and microwave engineering and applies them to high-speed digital design—creating the optimal combination between theory and practical applications.

#### Bayesian Signal Processing: Classical, Modern and Particle Filtering Methods

#### James V. Candy

9780470180945 • Cloth • 445pp • \$130.00 • April 2009 Wiley-IEEE Press

This text enables readers to fully exploit the many advantages of the "Bayesian approach" to model-based signal processing. It clearly demonstrates the features of this powerful approach compared to the pure statistical methods found in

1AXWELL'S

OUATIONS

other texts. Readers will discover how easily and effectively the Bayesian approach, coupled with the hierarchy of physics-based models developed throughout, can be applied to signal processing problems that previously seemed unsolvable.

#### **Maxwell's Equations**

#### Paul G. Huray

9780470542767 • Cloth • 312pp • \$110.00 • November 2009 Wiley-IEEE Press

Maxwell's Equations is a practical guide to one of the most remarkable sets of equations ever devised. Professor Paul Huray presents techniques that show the reader how to obtain analytic solutions for Maxwell's equations for ideal materials and

boundary conditions. These solutions are then used as a benchmark for solving real-world problems.

Order Information 1 (877) 762-2974 North America + 44 (0) 1243 843294 in Rest of World Log on to www.wiley.com

#### The Foundations of Signal Integrity Paul G. Hurav

9780470343609 • Cloth • 339pp • \$125.00 • November 2009 Wiley-IEEE Press

The Foundations of Signal Integrity is the first of its kind—a reference that examines the physical foundation of system integrity based on electromagnetic theory derived from Maxwell's Equations. Drawing upon the cutting-edge research of Professor Paul

Huray's team of industrial engineers and graduate students, it develops the physical theory of wave propagation using methods of solid state and high-energy physics, mathematics, chemistry, and electrical engineering before addressing its application to modern high-speed systems.

#### Handbook on Array Processing and Sensor Networks Simon Haykin, K. J. Ray Liu

9780470371763 • Cloth • 904pp • \$185.00 • January 2010 Wiley-IEEE Press

Featuring contributions by world-renowned experts in their fields, Handbook on Sensor and Array Processing collects tutorial articles on recent advancements and state-ofthe-art results by providing a comprehensive overview of

sensor and array processing. This first published book on the subject covers fundamental principles as well as applications, making it a must have for researchers, professors, graduate students, and practitioners.

#### Adaptive Signal Processing: Next Generation Solutions Tulay Adali, Simon Haykin

9780470195178 • Cloth • 424pp • \$135.00 • March 2010 Wiley-IEEE Press

This book presents the latest research results in adaptive signal processing with an emphasis on important applications and theoretical advancements. Each chapter is self-contained, comprehensive in its coverage, and written by a leader in his or her field of specialty. A uniform style is maintained throughout the book and each chapter concludes with problems for readers to reinforce their understanding of the material presented. The book can be used as a reliable reference for researchers and practitioners or as a textbook for graduate students.

WILEY **WILEY**

#### Advanced Digital Signal Processing and Noise Reduction, 4th Edition Saeed V. Vaseghi

9780470754061 • Cloth • 544pp • \$150.00 • March 2009 Wiley

The fourth edition of Advanced Digital Signal Processing and Noise Reduction updates and extends the chapters in the previous edition and includes two new chapters on MIMO systems, Correlation and Eigen analysis and

independent component analysis. The wide range of topics covered in this book include Wiener filters, echo cancellation, channel equalisation, spectral estimation, detection and removal of impulsive and transient noise, interpolation of missing data segments, speech enhancement and noise/interference in mobile communication environments. This book provides a coherent and structured presentation of the theory and applications of statistical signal processing and noise reduction methods.

#### Complex Valued Nonlinear Adaptive Filters: Noncircularity, Widely Linear and Neural Models

Danilo Mandic, Vanessa Su Lee Goh 9780470066355 • Cloth • 344pp • \$150.00 • June 2009 Wiley

This book was written in response to the growing demand for a text that provides a unified treatment of linear and nonlinear complex valued adaptive filters, and methods for the processing of general complex signals (circular

and noncircular). It brings together adaptive filtering algorithms for feedforward (transversal) and feedback architectures and the recent developments in the statistics of complex variable, under the powerful frameworks of CR (Wirtinger) calculus and augmented complex statistics. This offers a number of theoretical performance gains, which is illustrated on both stochastic gradient algorithms, such as the augmented complex least mean square (ACLMS), and those based on Kalman filters. This work is supported by a number of simulations using synthetic and real world data, including the noncircular and intermittent radar and wind signals.

CMass

#### society NEWS continued

multimodal and biomedical problems; and applications with direct societal relevance. He has published over 350 papers and has seven granted and ten pending U.S. patents.

Dr. Narayanan's lecture topics include the following:

Human-Centered Speech and Audio

Processing

Expressive Human Communication:

Automatic Recognition and Synthesis

Speech-to-Speech Translation: Advances, Challenges, and Opportunities

Speech Production: Data, Models and Technology Applications

Designing Multimodal Interfaces for Children

Multimodal Behavioral Signal Processing.

#### ANTONIO ORTEGA

Antonio Ortega received the telecommunications engineering degree, Universidad Politecnica de Madrid, Spain in 1989 and the Ph.D. in electrical engineering, Columbia University, New York, in 1994. In 1994, Dr. Ortega joined the Electrical Engineering-Systems Department, University of Southern California (USC), where he is currently a professor and associate chair of Electrical Engineering Systems. He has served as director, Signal and Image Processing Institute at USC.

He is an IEEE Fellow and a member of ACM. He has been chair and member. Image, Video, and Multidimensional Signal Processing Technical Committee (2004-2005) and (2006-present), respectively; and member, SPS Board of Governors (2002). He has been Technical Program cochair of ICIP 2008, MMSP 1998, and ICME 2002. He is associate editor, IEEE Transactions on Image Processing (2007-2010) and area editor (feature articles), IEEE Signal Processing Magazine (2009-present). He was also associate editor, IEEE Signal Processing Letters (2001-2002) and EURASIP Journal on Advances in Signal Processing. He received the NSF CAREER Award, the IEEE Communications Society Leonard G. Abraham Prize Paper Award (1997), the IEEE Signal Processing Society Magazine Award (1999), and the EURASIP Journal of Advances in Signal Processing Best Paper Award (2006).

His research interests are multimedia compression, communications, and signal

analysis. His recent work is focusing on distributed compression, multiview coding, error tolerant compression, wavelet-based signal analysis, and information representation in wireless sensor networks.

Dr. Ortega's lecture topics include the following:

Practical Applications of Distributed Source Coding

- Multiview Video: Coding Efficiency and Flexible Decoding

- Wavelets on Graphs and Trees: Constructions and Applications

Seeing the Signals: Applying Signal Processing Tools to Real World Data Analysis Problems.

#### VENUGOPAL V. VEERAVALLI

Venugopal V. Veeravalli received the Ph.D. degree from the University of Illinois at Urbana-Champaign (1992), the M.S. degree from Carnegie-Mellon University, Pittsburgh, Pennsylvania (1987), and the B.Tech. degree from the Indian Institute of Technology, Bombay (1985), all in electrical engineering. He joined the University of Illinois at Urbana-Champaign in 2000, where he is currently professor, Department of Electrical and Computer Engineering, and research professor, Coordinated Science Laboratory. He is also director, Illinois Center for Wireless Systems (ICWS). He was program director for Communications Research, U.S. National Science Foundation in Arlington, Virginia (2003-2005). He has held academic positions at Harvard University, Rice University, and Cornell University and has been on sabbatical at MIT, IISc Bangalore, and Qualcomm, Inc.

His research interests include distributed sensor systems and networks, wireless communications, detection and estimation theory, and information theory. He is an IEEE Fellow. He was on the Board of Governors of the IEEE Information Theory Society (2004– 2007) and associate editor of *IEEE Transactions on Information Theory* (2000– 2003) and *IEEE Transactions on Wireless Communications* (1999–2000). He is on the editorial boards of *Communications in Information and Systems* and *Journal of Statistical Theory and Practice.*

He received the IEEE Browder J. Thompson Best Paper Award (1996); the National Science Foundation CAREER Award (1998); the Presidential Early Career Award for Scientists and Engineers (PECASE) (1999); the Michael Tien Excellence in Teaching Award from the College of Engineering, Cornell University (1999); and the Xerox Award for faculty research from the College of Engineering, University of Illinois (2003).

Dr. Veeravalli's lecture topics include the following:

- Quickest Change Detection with Distributed Sensors and Its Applications

- Smart Sleeping Policies for Inference in Sensor Networks

- Distributed Regression and Estimation in Sensor Networks

Dynamic Spectrum Access with Learning for Cognitive Radio

Interference Management in Wireless Networks.

#### ABDELHAK M. ZOUBIR

Abdelhak M. Zoubir received his Dr.-Ing. from Ruhr-Universität Bochum, Germany, in 1992. He was associate professor, Queensland University of Technology, Australia (1992–1998); professor of telecommunications, Curtin University of Technology, Australia (1999); interim head, School of Electrical and Computer Engineering (2001–2003); professor and head of the Signal Processing Group, Technische Universität Darmstadt, Germany (2003).

His research interests are statistical methods for signal processing with emphasis on bootstrap techniques, robust detection and estimation and array processing applied to telecommunications, radar, sonar, car engine monitoring, and biomedicine. He published over 300 journal and conference papers on these areas. He coauthored Bootstrap Techniques for Signal Processing (Cambridge University Press, 2004), and he was a guest editor of a special issue on the bootstrap and its applications in IEEE Signal Processing Magazine (2007). He coauthored the paper "Detection of Sources Using Bootstrap Techniques," which received the 2003 IEEE SPS Young Author Best Paper Award.

He was deputy technical chair (plenary and special sessions), IEEE International Conference on Acoustics, Speech, and Signal Processing (ICASSP 1994); technical chair,

IEEE SIGNAL PROCESSING MAGAZINE [8] MARCH 2010

IEEE Workshop on Statistical Signal Processing (SSP 2001); general cochair, IEEE International Symposium on Signal Processing & Information Technology (ISSPIT 2003); and general cochair, IEEE Workshop on Sensor Array and Multichannel Signal Processing (SAM 2008). He was the plenary sessions cochair, ICASSP 2008. He was associate editor, IEEE Transactions on Signal Processing (1999-2005), and he is on the editorial boards of Signal Processing and the Journal on Advances in Signal Processing. He has been an editorial board member, IEEE Journal on Selected Topics in Signal Processing (2009); member, Signal Processing Theory and Methods Technical Committee (2002); vice-chair (2008-2009); and chair (2010-2011); member, Sensor Array and Multichannel Signal Processing Technical Committee (2007-present); member, Signal Processing Education Technical Committee (2006-2008): and an elected member, AdCom for the European Association for Signal and Image Processing.

Dr. Zoubir's lecture topics include the following:

Source Separation for Nonstationary Signals

The Bootstrap Paradigm in Signal Processing: Estimation, Detection, and Model Selection

Robust Statistics for Parameter

Estimation and Signal Detection

Signal Processing for Automotive Monitoring.

#### 38 SPS MEMBERS ELEVATED TO FELLOW

Each year, the IEEE Board of Directors confers the grade of Fellow on up to one-tenth percent of the members. To be considered, an individual must have been a Member, normally for five years or more, and a Senior Member at the time for nomination to Fellow. The grade of Fellow recognizes unusual distinction in IEEE's designated fields.

The SPS congratulates these 38 SPS members who were recognized with the grade of Fellow as of 1 January 2010.

*Martin J. Bastiaans*, Eindhoven, The Netherlands: For contributions to signal processing for optical signals and systems.

*Lorenzo Bruzzone*, Trento, Italy: For contributions to pattern recognition and image processing for remote sensing.

*Ahmet Enis Cetin*, Ankara, MN, Turkey: For contributions to signal recovery and image analysis algorithms.

*Laurent Cohen*, Neuilly-Sur-Seine, France: For contributions to computer vision technology for medical imaging.

*David Daniels,* Leatherhead, Surrey, United Kingdom: For contributions to ground-penetrating radar.

*Michel Defrise*, Brussels, Belgium: For contributions to computer tomography.

*Ray Dolby,* San Francisco, California: For leadership in developing and commercializing practical noise reduction technology.

*Hesham M. El-Gamal,* Columbus, Ohio: For contributions to multiple-input multiple-output and cooperative communications.

*Mário Alexandre Teles Figueiredo*, Lisboa, Portugal: For contributions to pattern recognition and computer vision.

*Daniel R. Fuhrmann,* Houghton, Michigan: For contributions to adaptive radar signal processing.

*Marc Hillel Goldburg*, Redwood City, California: For leadership in the development and commercialization of spectrally efficient wireless communications systems.

*Matti A. Karjalainen*, Espoo, Finland: For contributions to perceptual audio signal modeling and processing.

*Bart Kosko*, Los Angeles, California: For contributions to neural and fuzzy systems.

*B.V.K. Vijaya Kumar*, Pittsburgh, Pennsylvania: For contributions to biometric recognition methods.

Andrew Francis Laine, New York: For contributions to wavelet applications in digital mammography and ultrasound image analysis.

*Seong-Whan Lee*, Seoul, Korea: For contributions to pattern recognition for biometrics and document image analysis.

*Peyman Milanfar*, Santa Cruz, California: For contributions to inverse problems and super-resolution in imaging.

*Randolph Lyle Moses*, Columbus, Ohio: For contributions to statistical signal processing.

Aria Nosratinia, Richardson, Texas: For contributions to multimedia and wireless communications.

*Robert Nowak*, Madison, Wisconsin: For contributions to statistical signal and image processing. *Roberto Pieraccini,* New York: For contributions to statistical natural language understanding and spoken dialog management and learning.

*Douglas A. Reynolds*, Lexington, Massachusetts: For contributions to Gaussian-mixture-model techniques for automatic speaker recognition.

*Giuseppe Riccardi*, Povo-Trento, Italy: For contributions to algorithms for automatic speech recognition and spoken language processing.

*Yong Rui,* Beijing, China: For contributions to image and video analysis, indexing, and retrieval.

*Motoyuki Sato*, Sendai, Miyagi-ken, Japan: For contributions to radar remote sensing technologies in environmental and humanitarian applications.

*Mihaela Schaar,* Los Angeles, California: For contributions to multimedia compression and communications.

*Robert Schober*, Vancouver, BC, Canada: For contributions to wireless communications.

*Dan Schonfeld*, Glenview, Illinois: For contributions to image and video analysis.

Andrew C. Singer, Urbana, Illinois: For contributions to signal processing techniques for digital communication.

*Malcolm Graham Slaney,* Palo Alto, California: For contributions to perceptual signal processing and tomographic imaging.

*Frank K. Soong*, Beijing, China: For contributions to speech processing.

*Milica Stojanovic*, Boston, Massachusetts: For contributions to underwater acoustic communications.

Daniel Trudnowski, Butte, Montana: For contributions to algorithms for characterizing power-system small-signal stability properties.

*Vishu R. Viswanathan*, Plano, Texas: For contributions to speech coding and synthesis and objective speech quality evaluation.

*Howard C. Yang*, Shanghai, China: For leadership in mixed-signal integrated circuit design and manufacturing.

*Feng Zhao*, Issaquah, Washington: For contributions to networked embedded computing and sensor networks.

*Wenwu Zhu*, Beijing, China: For contributions to video communications over the internet and wireless.

IEEE SIGNAL PROCESSING MAGAZINE [9] MARCH 2010

society NEWS continued

*Xinhua Zhuang*, Columbia, Missouri: For contributions made to digital image processing, image coding, and computer vision.

The following individual was evaluated by the SPS, but is not an SPS member:

Alevoor Ravishankar Rao, Yorktown Heights, New York: For contributions to understanding of image texture and applications to machine vision solutions.

#### CALL FOR NOMINATIONS: REGIONAL DIRECTORS-AT-LARGE AND BOARD OF GOVERNORS MEMBERS-AT-LARGE

In accordance with the SPS Bylaws, the membership will elect, by direct ballot, three members-at-large to the Board of Governors for three-year terms commencing 1 January 2011 and ending 31 December 2013, as well as one regional director-at-large for the corresponding regions: Regions 1–6 (U.S.), Regions 7 and 9 (Canada and Latin America), Region 8 (Europe/Middle East/Africa) and Region 10 (Asia/Pacific Rim) for two-year terms commencing 1 January 2011 and ending 31 December 2012.

Regional directors-at-large are elected locally by members of the corresponding region. They serve as nonvoting members of the Board of Governors and voting members of the Membership Board. They promote and foster local activities and encourage new chapter development; represent their regions to the core of SPS; offer advice to improve membership relations, provide recruiting and service to their regions; guide and work with their corresponding chapters to serve their members; and assist the vice president-Awards in conducting chapter reviews.

Board of Governors members-at-large are directly elected by the Society's membership to represent the member viewpoint in Board decision making. They typically review, discuss, and act upon a wide range of items affecting the actions, activities, and health of the Society.

José M.F. Moura, SPS past president and chair of the Nominations and Appointments (N&A) Committee, has provided the following formal procedures for the SPS's 2010 regional directors-at-large and BoG members-at-large elections. Publication of a call for nominations for positions of BoG members-at-large and regional directors-at-large. Nominees must hold SPS Member grade (IEEE Member grade or higher and Member of SPS) to hold elective office (March).

From the responses received, a list of candidates will be assembled for each election by the past president for presentation to the N&A Committee (April).

The N&A Committee ballots to create a short list of at least six candidates (by bylaw, at least two candidates must be submitted for each BoG member-at-large position becoming vacant) (April–May). Currently, there is no minimum number of candidates required for the regional directors-at-large race. Nevertheless, the Society has a stated preference for contested elections, so more than one nomination per race is desirable.

After the N&A ranking ballot, the top candidates who are willing and able to serve for director-at-large and member-at-large are advanced for ballot to the SPS's voting members (July).

Collection and tabulation of returned ballots will again be handled by the IEEE Technical Activities Society Services Department on behalf of the SPS (July–September).

The three candidates receiving the highest number of votes who confirm their ability to serve will be declared elected members-at-large to the Board of Governors with three-year terms commencing 1 January 2011 and one candidate from each specified region receiving the highest number of votes who confirm their ability to serve will be declared elected a regional directorat-large with a two-year term commencing 1 January 2011 (September).

Please provide nominations for regional director-at-large and member-at-large to Past President José M.F. Moura via e-mail to <u>t.argiropoulos@ieee.org</u> or via fax to +1 732 235 1627. Please provide the name, address, phone, fax, e-mail, or other contact information of the nominee, along with a brief background on the individual (no more than 100 words, please) and any information about the individual's current

activities in the SPS, IEEE, or other professional societies.

#### 2009 IEEE SPS AWARDS PRESENTED IN DALLAS, TEXAS

The IEEE SPS congratulates the SPS members who received the Society's prestigious awards during ICASSP 2010 in Dallas, Texas.

The Society Award honors outstanding technical contributions in a field within the scope of the IEEE SPS and outstanding leadership in that field. The Society Award comprises a plaque, a certificate, and a monetary award of US\$2,500. It is the highest-level award bestowed by the IEEE SPS. This year's recipient was Rama Chellappa "for pioneering and fundamental contributions to image and videobased analysis and understanding."

The IEEE Signal Processing Magazine Best Paper Award honors the author(s) of an article of exceptional merit and broad interest on a subject related to the Society's technical scope and appearing in the Society's magazine. The prize comprises US\$500 per author (up to a maximum of US\$1,500 per award) and a certificate. If there are more than three authors, the maximum prize shall be divided equally among all authors and each shall receive a certificate. The 2009 IEEE Signal Processing Magazine Best Paper Award recipients are Neal Patwari, Joshua N. Ash, Spyros Kyperountas, Alfred O. Hero, III, Randolph L. Moses, and Neiyer S. Correal, for the article "Locating the Nodes: Cooperative Localization in Wireless Sensor Networks," IEEE Signal Processing Magazine, vol. 22, no. 4, July 2005.

The IEEE Signal Processing Magazine Best Column Award honors the author(s) of a column of exceptional merit and broad interest on a subject related to the Society's technical scope and appearing in the Society's magazine. The prize shall consist of US\$500 per author (up to a maximum of US\$1,500 per award) and a certificate. If there are more than three authors, the maximum prize shall be divided equally among all authors and each shall receive a certificate. This year's IEEE Signal Processing Magazine Best Column Award recipient is Richard G. Baraniuk, for the article "Compressive Sensing [Lecture

IEEE SIGNAL PROCESSING MAGAZINE [10] MARCH 2010

#### Notes]," in *IEEE Signal Processing Magazine*, vol. 24, no. 4, July 2007.

Two Technical Achievement Awards were presented this year. Alan S. Willsky received the award "for originality and innovation in stochastic multiresolution modeling in statistical and graphical modeling, and in probabilistic control-driven signal processing." K.J. Ray Liu was recognized "for pioneering and outstanding contributions for the advances of signal processing in multimedia forensics, security, and wireless communications." The Technical Achievement Award honors a person who, over a period of years, has made outstanding technical contributions to the theory and/or practice in technical areas within the scope of the Society, as demonstrated by publications, patents, or recognized impact on this field. The prize is a monetary award of US\$1,500, a plaque, and a certificate.

The Meritorious Service Award was presented this year to Arye Nehorai "for exceptional and dedicated service as a leader in a broad range of activities for the Society and profession" and to Isabel Maria Martins Trancoso "for outstanding service and leadership to the worldwide community in the field of speech processing." The award comprises a plaque and a certificate; judging is based on dedication, effort, and contributions to the Society.

The SPS Education Award honors educators who have made pioneering and significant contributions to signal processing education. Judging is based on a career of meritorious achievement in signal processing education as exemplified by writing of scholarly books and texts, course materials, and papers on education; inspirational and innovative teaching; and creativity in the development of new curricula and methodology. The award comprises a plaque, a monetary award of US\$1,500, and a certificate. The recipient of the SPS Education Award is Robert M. Gray "for outstanding contributions to education and mentoring in signal processing."

Six Best Paper Awards were awarded, honoring the author(s) of a paper of exceptional merit dealing with a subject related to the Society's technical scope, and appearing in one of the Society's transactions, irrespective of the author's age. The prize is US\$500 per author (up to a maximum of US\$1,500 per award), and a certificate. Eligibility is based on a five-year window preceding the year of election, and judging is based on general quality, originality, subject matter, and timeliness. Up to six Best Paper Awards may be presented each year. This year, the awardees were:

Zhou Wang, Alan Conrad Bovik, Hamid Rahim Sheikh, and Eero P. Simoncelli, "Image Quality Assessment: From Error Visibility to Structural Similarity," *IEEE Transactions on Image Processing*, vol. 13, no. 4, Apr. 2004.

Zhi-Quan (Tom) Luo and Shuzhong Zhang, "Dynamic Spectrum Management: Complexity and Duality," *IEEE Journal of Selected Topics in Signal Processing*, vol. 2, no. 1, Feb. 2008.

Quentin H. Spencer, A. Lee Swindlehurst, and Martin Haardt, "Zero-Forcing Methods for Downlink Spatial Multiplexing in Multiuser MIMO Channels," *IEEE Transactions on Signal Processing*, vol. 52, no. 2, Feb. 2004.

Chul Min Lee and Shrikanth S. Narayanan, "Toward Detecting Emotions in Spoken Dialogs," *IEEE Transactions on Speech and Audio Processing*, vol. 13, no. 2, Mar. 2005.

Jan Lukáš, Jessica Fridrich, and Miroslav Goljan, "Digital Camera Identification from Sensor Pattern Noise," *IEEE Transactions on Information Forensics and Security*, vol. 1, no. 2, June 2006.

Genyuan Wang and Moeness G. Amin, "Imaging Through Unknown Walls Using Different Standoff Distances," *IEEE Transactions on Signal Processing*, vol. 54, no. 10, Oct. 2006.

The Young Author Best Paper Award honors the author(s) of an especially meritorious paper dealing with a subject related to the Society's technical scope and appearing in one of the Society's transactions and who, upon date of submission of the paper, is less than 30 years of age. Eligibility is based on a three-year window preceding the year of election, and judging is based on general quality, originality, subject matter, and timeliness. Two Young Author Best Paper Awards were presented this year:

Mags

Tomoki Toda, for the paper coauthored with Alan W. Black and Keiichi Tokuda, "Voice Conversion Based on Maximum-Likelihood Estimation of Spectral Parameter Trajectory," *IEEE Transactions on Audio, Speech, and Language Processing*, vol. 15, no. 8, November 2007.

Florian Luisier, for the paper coauthored with Thierry Blu and Michael Unser, "A New SURE Approach to Image Denoising: Interscale Orthonormal Wavelet Thresholding," *IEEE Transactions on Image Processing*, vol. 16, no. 3, March 2007.

#### SPS MEMBERS RECEIVE IEEE AWARDS

Ronald Schafer has been selected as the IEEE Jack S. Kilby Signal Processing Medal recipient "for leadership and pioneering contributions to the field of digital signal processing." The medal will be presented to Prof. Schafer at the IEEE Honors Ceremonies.

The James L. Flanagan Speech and Audio Processing Technical Field Award will be presented to Prof. Sadaoki Furui "for contributions to and leadership in the field of speech and speaker recognition towards natural communication between humans and machines." This award was founded and is sponsored by the IEEE SPS.

*The IEEE Alexander Graham Bell Medal* will be presented to Prof. John M. Cioffi "for pioneering discrete multitone modem technology as the foundation of the global DSL industry."

The IEEE Edison Medal will be presented to Prof. Ray Dolby "for leadership and pioneering applications in audio recording and playback equipment for both professional and consumer electronics."

The IEEE Dennis J. Picard Medal for Radar Technologies and Applications will be presented to Prof. Alfonso Farina "for continuous, innovative, theoretical and practical contributions to radar systems and adaptive signal processing techniques."

SP]

Ron Schneiderman

# SETI–Are We (Still) Alone?

t's an age-old question: Are we alone in the universe?

The fact is, we still don't know for sure. But that hasn't stopped us from looking. And we're looking harder than ever.

Movies like *The Day the Earth Stood Still* (1951), *Close Encounters* (1977), and more recently *District 9*, which has been described in reviews as a social satire about a spacecraft that stalls over Johannesburg, have all been box office hits—a pretty strong indication what we all still want to know: Is anyone else out there?

Be assured that a lot of highly qualified people are still trying to find out.

"When we do radio search for extraterrestrial intelligence (SETI), what we're looking for is a narrowband signal with one spot on the radio dial. That's been true ever since Frank Drake—since that first experiment in 1960," says Seth Shostak, senior astronomer for the SETI Institute, based in Mountain View, California. That's the kind of signal where you pump all of your transmitter power into 1 Hz on the dial. "That's what we traditionally look for," says Shostak.

The way to find those, he says, is the incoming cosmic static to your antenna. "It's just Fourier-transformed and you look for a whole bunch of energy, a whole bunch of power. It's the kind of signal that's nonnatural. We get a lot of radio static from the cosmos—quasars, pulsars, hot gas, cold gas, even Saturn and Jupiter and the Sun; they all make a lot of radio noise. But it's not narrowband. So, it would easily be distinguished from the natural static."

#### DRAKE'S EQUATION

Dr. Frank Drake (formerly the board chair of the SETI Institute, and still involved in

Digital Object Identifier 10.1109/MSP.2009.935382

SETI activities) was a young astronomer working at the National Radio Astronomy Observatory in Green Bank, Virginia, when he estimated the number of technical civilizations that may exist in the galaxy. It quickly became known as the Drake equation, and identifies specific factors thought to play a role in the development of these civilizations although, after years of searching, some SETI scientists aren't as comfortable with Drake's thinking as they used to be. The equation, first presented by Drake in 1961, was originally written as  $N = R^*$ . fp. ne. fl. fi. fc. L, where

N = is the number of civilizations in the Milky Way Galaxy whose electromagnetic emissions are detectable.

R\* is the rate of formation of stars suitable for the development of intelligent life.

■ fp is the fraction of those stars with planetary systems.

ne equals the number of planets, per solar system, with an environment suitable for life.

■ fl is the fraction of life-bearing planets on which intelligent life emerges.

fi equals the fraction of life-bearing planets on which intelligent life emerges.

fc is the fraction of civilizations that develop a technology that releases detectable signs of their existence into space.

• L is the length of time such civilizations release detectable signals into space.

#### A NEW TELESCOPE ARRAY

A lot has changed since 1961. In early 2007, the SETI Institute and the University of California (UC)-Berkeley, which works closely with the institute and has its own major SETI program, activated an entirely new system for searching for extraterrestrial intelligence, the Allen telescope array (ATA) (see Figure 1).

The ATA is a network of 42 6-m diameter, mass-produced radio dishes, but the plan is to increase the array to 350 telescopes over the next three years. That is, if the institute and UC-Berkeley can get them funded.

The total cost of the project to date, including research, development, and

[FIG1] The ATA, activated in October 2007, is a joint project of UC-Berkeley and the SETI Institute. Currently made up of 42 radio dishes, the system is expected to grow to 350 dishes to advance the search for extraterrestrial life and radio astronomy research.

IEEE SIGNAL PROCESSING MAGAZINE [12] MARCH 2010

1053-5888/10/\$26.00©2010IEEE

**q**Mags

construction of the array and the necessary radio astronomy and SETI signal detectors, was US\$50 million. About half of that seed money was donated by Microsoft Cofounder Paul G. Allen. Additional funding has come from the SETI Institute, UC-Berkeley, the National Science Foundation, former Microsoft chief scientist Nathan Myhrvold, Greg Papadopoulos, Xilinx, and other corporations and individual donors.

Completing the array is expected to cost about another US\$40 million. Although dona-

tions are welcome, the SETI Institute and UC-Berkeley hope to speed up the completion process with a proposal that they submitted to the National Science Foundation in August 2009, which would double the size of the ATA.

While still somewhat limited in sensitivity, a fully developed ATA would significantly expand the radio frequency band for conducting the search, and could detect fainter and more distant signals with more telescopes. At 4.5 octaves of frequency, it already can collect a fairly large amount of data.

The current array of 42 dishes is spread out over an area of about a half a kilometer. Located near the town of Hat Creek, just north of Lassen Volcanic National Park in northern California, the dishes working together can take in five square degrees of sky at a time—a box as wide as ten full moons. For SETI, in particular, this means that over the next few dozen years, the ATA will get a thousand times more data than has been accumulated in the past 45 years (see Figure 2).

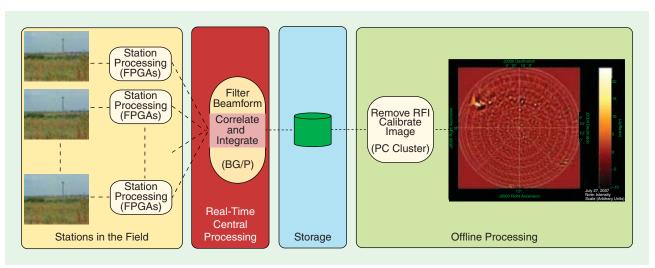

"What you need to do," says Shostak, "is to cross-correlate the antennas. They're putting out streams of bits and you want to correlate them. You want to multiply a string of bits from one antenna against another and that means you can't have them very far apart." (See Figure 3.)

Unlike previous telescopes used in SETI programs, the ATA has several features designed specifically for the

[FIG2] This log periodic dual polarization feed covers 0.5–11.2 GHz. Each of the feeds from the 42 telescopes in the array outputs an equivalent of 200 GB/s.

SETI mission, including one that filters out noise from man-made interference that in many radio telescopes would render much of the data unusable.

What ATA managers didn't anticipate was interest from the U.S. Air Force Space Command (AFSC), which sees the array as a way to expand its space surveillance capability. "The Air Force is interested in the technology, not the aliens," notes Shostak, and that essentially means adopting the additional sensors provided by the ATA to observe orbiting objects during the day. Because

[FIG3] Seth Shostak, a senior astronomer with the Mountain View, California-based SETI Institute, says he expects the ATA (named after Paul Allen, the cofounder of Microsoft) to produce a thousand times more data over the next few dozen years than has been accumulated in the past 45 years.

its electro-optical sensors are affected by light pollution during the day, limiting observations that can be conducted at that time, most of the ATA's primary mission is conducted at night. This gives the array its best pointing stability and avoids a decrease in strength of narrowband signals that comes from scattering by the solar wind. Mass

Initial tests run by the Air Force suggests the ATA could track transmitting communication satellites in low- and medium-Earth orbits and, most promising, in geosynchronous orbit, home to the

most costly and highly utilized satellites that orbit Earth. If demonstrations are successful, the AFSC says the ATA may prove to be a viable all-weather, day and night contributor to its space surveillance network.

#### WHO ELSE IS LOOKING?

The UC-Berkeley search, called the Search for Extraterrestrial Radio Emissions from Nearby Developed Intelligent Populations (SERENDIP), is run out of the Arecibo Observatory in Puerto Rico, which in the past has been used part-time by the SETI Institute. Other long-time programs include the Planetary Society, an independent, privately funded organization, which operates Project BETA at Harvard University as well as in Argentina. Ohio State University has been conducting a fulltime search for years with a large volunteer staff. Other much smaller and private SETI programs are underway in Italy and Australia, although they're not believed to be well funded.

Shostak says one of the most interesting SETI data-processing developments in the last few years is a suggested replacement for the Fourier transform currently used to analyze radio spectra with the Koenen-Loeuve transform, a concept being promoted in Italy that theoretically could simultaneously tap into both narrow and broadband (including spread-spectrum) signals. Italy is an active member of the

#### spotlight **REPORT** continued

International Academy of Astronautics' SETI Permanent Study Group.

Australia's Commonwealth Scientific and Industrial Research Organization commissioned the Parkes Observatory in the 1970s and has become legendarv in astronomical circles for its studies of radio galaxies, quasars, pulsars, and the Milky Way's nearest galactic neighbors, the Magellanic Clouds. At one point in the mid-1990s, the SETI Institute had 24 active, funded projects going at Parkes with a staff of 80 people, but using the 64-m Parkes telescope for SETI activity is very low kev at this point. An Australian SETI team known as Southern SERENDIP is attempting to "piggyback" its search onto the Parkes Observatory's much larger, more broad-based, astronomy program.

A SETI program is also just getting underway in Korea that piggybacks onto a radio astronomy experiment that's running in that country. While they won't have the luxury of pointing the telescope wherever they want, the Korean SETI scientists have access to the data generated by the telescope to look for SETIlike signals.

#### TAKING SETI PERSONALLY

Another big SETI program, run by UC-Berkeley, is SETI@Home (see Figure 4).

Think of thousands of personal computers (PCs) all over the world, all work-

ing simultaneously to analyze different parts of data collected by the Arecibo telescope, which is the biggest single telescope on Earth.

Essentially, the SETI@ Home project borrows computer time from anyone who volunteers for the program when they aren't using their computers for other tasks. It does this with a screen saver that gets data from Berkeley over the Internet, analyzes that data, and then reports the results to Berkeley. The program is entirely voluntary. When you need your PC back, the Berkeley screen saver instantly shuts down and only continues its analysis when you're not using your PC. SETI@Home connects only when transferring data.

All of this is accomplished by breaking up the data into small pieces. Data is recorded on high-density tapes at Arecibo. Since Arecibo does not have a high bandwidth Internet connection, the data is sent to Berkeley very slowly where it is divided into 0.25-MB chunks (called "work units"). These are sent from the SETI@Home server over the Internet for analysis to people around the world.

UC Berkley keeps track of the workunits with a large database. Its computers look for new work units to be processed and these are sent out and marked "in progress" in its database. If you can't complete the work unit, or if your computer crashes and you lose your results, the data isn't lost.

#### WHERE'S NASA?

Where does NASA fit into all of this activity? For all of its interest in finding some form of life in space (most recently searching for traces of water on Mars and by firing a rocket into a crater of the moon) NASA has been eliminated from any SETI-specific activities by an act of Congress.

NASA established SETI programs as early as the late 1970s that evolved into a

SETR8home Client

restrial Intelligence at HOME

Utime The Stemmesz of

fairly ambitious program known as the High-Resolution Microwave Survey (HRMS). That came to a halt in 1993 when U.S. Senator Richard Bryan of Nevada, citing budget pressures, successfully introduced an amendment to a bill that eliminated all funding for the HRMS program. (HRMS amounted to less than 0.1% of NASA's annual budget.)

NASA does, however, support the SETI Institute's much less publicized research in astrobiology, and its new US\$600 million Kepler telescope could become an extremely important factor in the search for extraterrestrial intelligence.

Launched in March 2009, Kepler is designed to survey the Milky Way galaxy to search for Earth-size and smaller planets and determine how many of the billions of stars in our galaxy have such planets. SETI scientists believe that Earth-size planets in our galaxy offer the best chance for finding intelligent life in space.

To conduct its search, the Kepler Mission uses a specially designed 0.95-m diameter telescope that acts as a very sophisticated photometer to measure the size and orbit of every planet that passes in front of the more than 100,000 stars located in what astronomers believe is the most promising region of the Milky Way. Kepler has a very large field of view for an astronomical telescope—105 square degrees, which is comparable to the area of a

> hand held at arm's length. (The fields of view of most telescopes are less than one square degree.) Kepler needs that large a field to observe the large number of stars. It will look at the same star field for the entire mission and continuously and simultaneously monitor the brightness of the stars for the life of the mission, which is three and a half years.

er Stimin 27.1 m

THE NEXT BIG THING

The next big thing in the SETI community, although

when SETI@HOME PCs are idle. Data from the program is collected by the

[FIG4] This screensaver looks for specific pulse signals. It's part of the SETI@HOME project that links thousands of PCs of volunteers all over the

world, all working simultaneously to analyze different parts of data

Arecibo Observatory in Puerto Rico.

not designed specifically for searching for extraterrestrial civilizations, is a US\$2 billion project called the square kilometer array (SKA). This is a huge international effort to develop an aperture plane phased array with telescopes that can do many different astronomical observations simultaneously—including SETI—with a million square meters of collecting area.

The SKA is still in the design stage, but testing is already underway of prototype telescopes and new signal processing devices that will be used for cross-correlating the SKA antennas. The array is expected to cover a frequency range of  $\sim 0.1-\sim 20$  GHz, and involve at least two technologically different antenna concepts. When completed in the second half of the next decade, the SKA will be able to scan and map the sky with a sensitivity  $\sim 100$ times greater than is currently possible.

The project is partly funded by the European Community Sixth Framework Programme, with partners from 26 institutes in 13 countries.

Participants in the program haven't yet come up with the US\$2 billion needed to complete the SKA, but Dan Werthimer, director of the SETI program at UC Berkeley, says Europeans, Australians, and South Africans have put US\$100 million into the program. The U.S. effort, led by the National Science Foundation, has only advanced US\$12 million at this point. Werthimer calls this "prototyping money," which is being used primarily for technology development (see Figure 5).

With Arecibo doing a good job covering the northern hemisphere, Werthimer says the SKA will be built either in Australia or South Africa first, to cover the southern hemisphere, but also to place the new telescope in a very quiet location. "Finding a quiet place is important, but we're learning how to get rid of the radio frequency interference; it's all about signal processing." (See Figure 6.)

Werthimer adds, "We're doing a huge amount of work at Berkeley in collaboration with other groups trying to figure out how to build next-generation telescopes. Not just for SETI, but for other kinds of astronomy, too. And it's

[FIG5] Dan Werthimer, director of the SETI program at UC-Berkeley, says his program SERENDIP is conducting a significant amount of work in collaboration with other interested groups in producing next-generation telescopes, with much of the focus on developing new techniques in signal processing. Arecibo is the world's largest radio telescope and is located in Puerto Rico. The group expects to spend about US\$300 million on signalprocessing development as part of its program.

[FIG6] These ATA racks are part of the scalable DSP instrumentation that are based largely on general-purpose FPGA signal processing boards developed by the Collaboration for Astronomy Signal Processing and Electronics Research (CASPER). (More information can be found at http://casper.berkeley.edu.)

dominated by signal processing. We expect to spend about US\$300 million on signal processing [development] as part of this program." Werthimer also says the SKA team is working with several companies, most

(continued on page 142)

Mass

IEEE SIGNAL PROCESSING MAGAZINE [15] MARCH 2010

#### reader's **CHOICE** Top Downloads in IEEE Xplore his issue's "Reader's Choice" the top 100 most downloaded IEEE ments are welcome and should be sent contains a list of articles Xplore articles from May to October to Associate Editor Berna Erol at berna published by the IEEE 2009. The highest rank obtained by erol@yahoo.com. Signal Processing Society an article in this time frame is indicated (SPS) that ranked among in bold. Your suggestions and com-SP **N TIMES RANK IN IEEE TOP 100** IN TOP (MAY-OCT 2009) TITLE, AUTHOR, PUBLICATION YEAR 100 SINCE **IEEE SPS JOURNALS** ABSTRACT ост SEP AUG JUL JUN MAY JAN 2006 COMPLEX WAVELET STRUCTURAL 7 The article introduces a new measure of 1 SIMILARITY: A NEW IMAGE image similarity that is called the complex wavelet structural similarity (CW-SSIM) index SIMILARITY INDEX Sampat, M.P.; Wang, Z.; Gupta, S.; and shows its applicability as a general Bovik, A.C.; Markey, M.K. purpose image similarity index. IEEE Transactions on Image Processing, vol.18, no. 11, Nov. 2009, pp. 2385-2401 A HISTOGRAM MODIFICATION FRAME-The paper presents a general framework 15 14 4 3 WORK AND ITS APPLICATION FOR based on histogram equalization for image contrast enhancement, where contrast IMAGE CONTRAST ENHANCEMENT enhancement is posed as an optimization Arici, T.; Dikbas, S.; Altunbasak, Y. problem that minimizes a cost function. IEEE Transactions on Image Processing, vol. 18, no. 9, Sep. 2009, pp. 1921–1935 FAST GRADIENT-BASED ALGORITHMS This paper studies gradient-based schemes 16 FOR CONSTRAINED TOTAL VARIATION for image denoising and deblurring problems IMAGE DENOISING AND DEBLURRING based on the discretized total variation (TV) minimization model with constraints. PROBLEMS Beck, A.; Teboulle, M. IEEE Transactions on Image Processing, vol. 18, no. 11, Nov. 2009, pp. 2419-2434 FROM LAGRANGE TO SHANNON ... AND This article examines the interplay between 25 2 2 BACK: ANOTHER LOOK AT SAMPLING analog and digital signals, casting discrete-Prandoni, P.; Vetterli, M. IEEE Signal Processing Magazine, time sequences in the lead role, with continuous-time signals entering the scene as a derived version of their gap-toothed vol. 26, no. 5, Sep. 2009, pp. 138-144 archetypes.

SAMPLING Candes, E.J.; Wakin, M.B. *IEEE Signal Processing Magazine,* vol. 25, no. 2, Mar. 2008, pp. 21–30

AN INTRODUCTION TO COMPRESSIVE

Digital Object Identifier 10.1109/MSP.2009.935420

IEEE SIGNAL PROCESSING MAGAZINE [16] MARCH 2010

16

34

61

35

56

65

18

1053-5888/10/\$26.00©2010IEEE

This article surveys the theory of compressive

sampling, also known as compressed sensing

or CS, a novel sensing/sampling paradigm

that goes against the common wisdom in

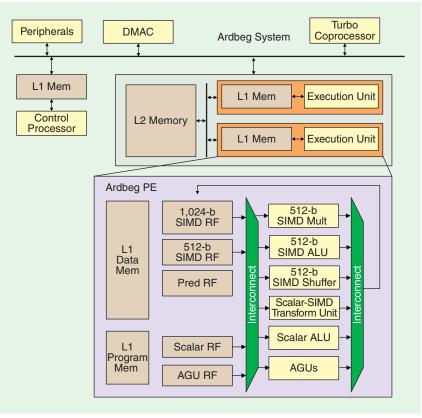

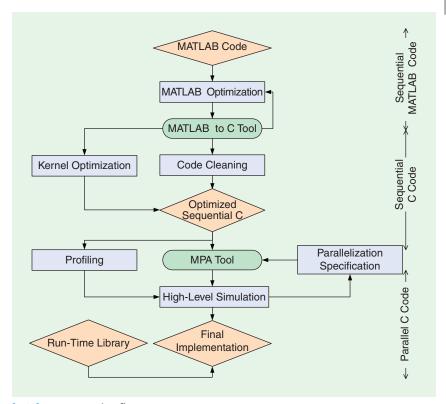

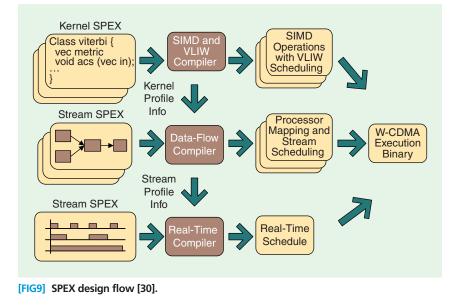

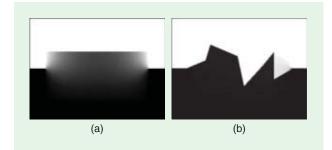

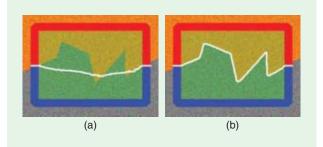

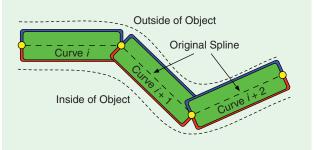

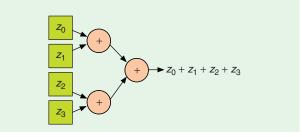

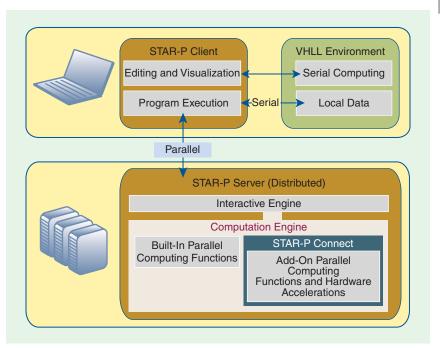

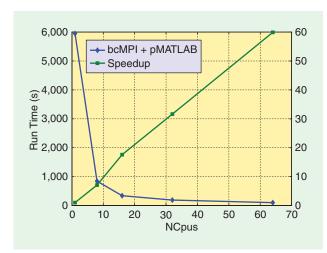

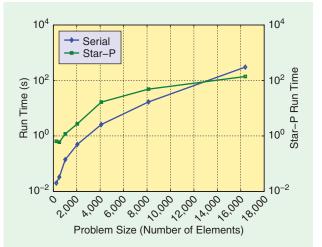

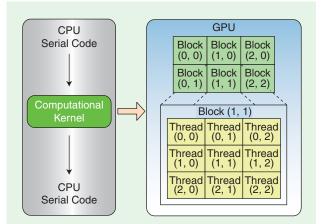

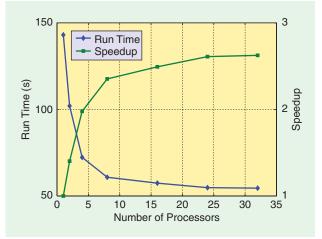

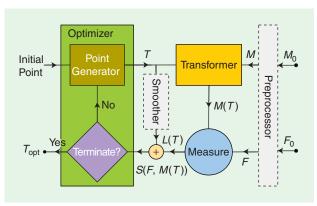

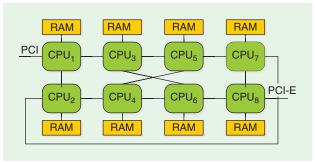

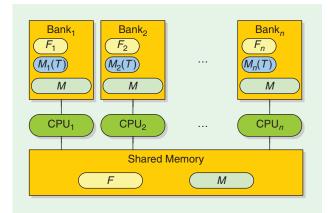

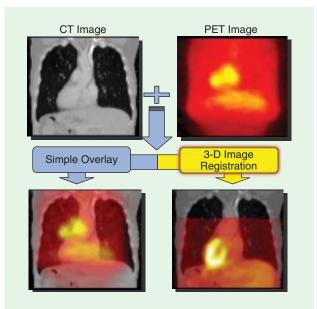

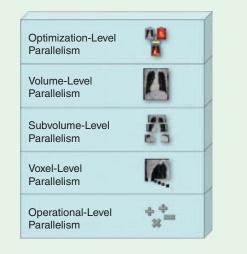

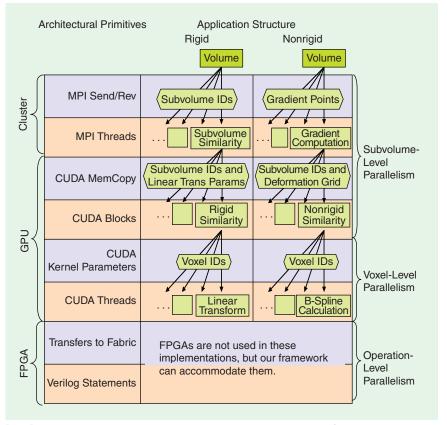

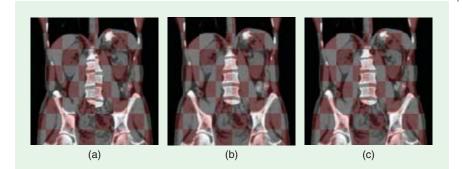

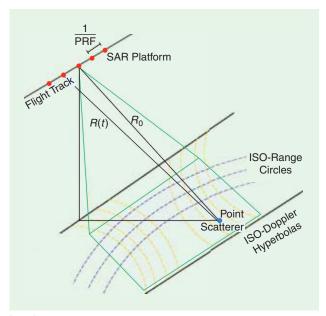

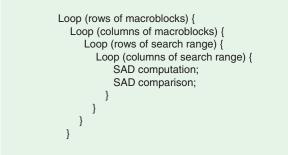

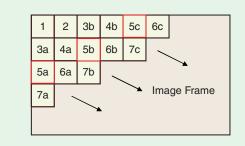

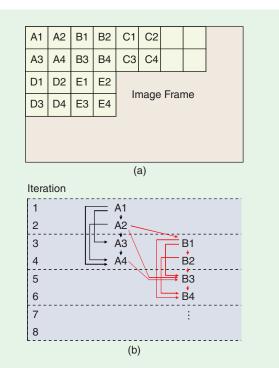

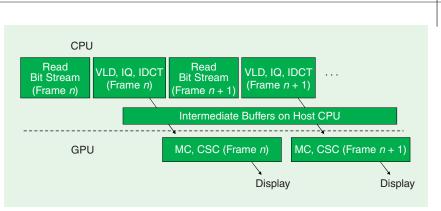

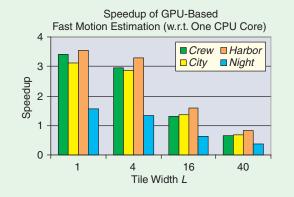

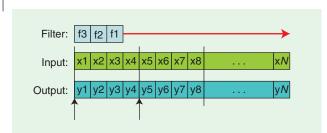

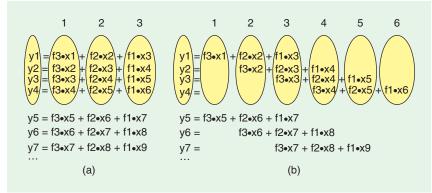

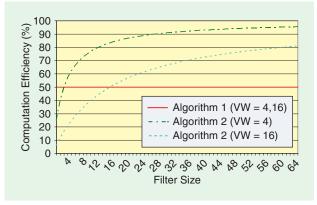

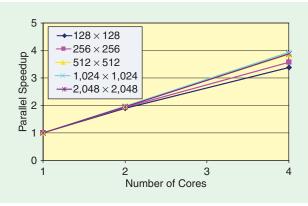

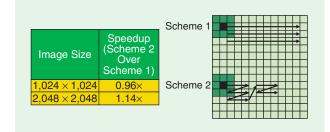

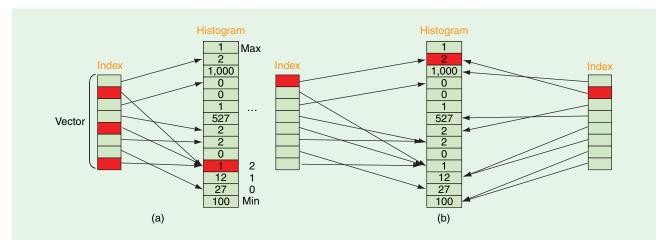

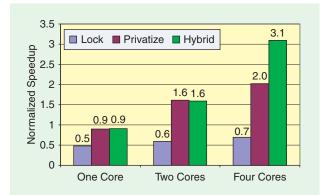

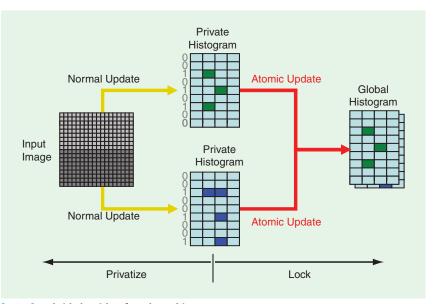

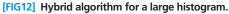

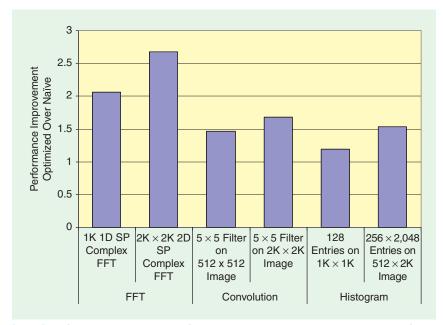

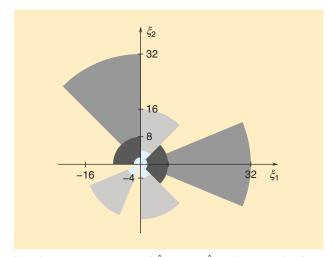

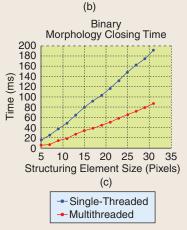

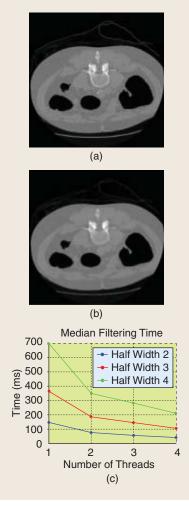

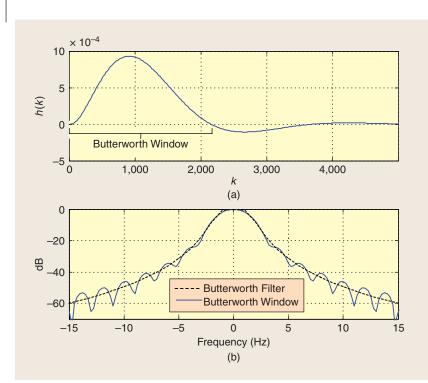

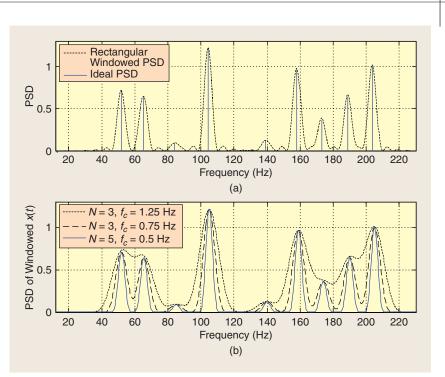

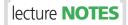

data acquisition.